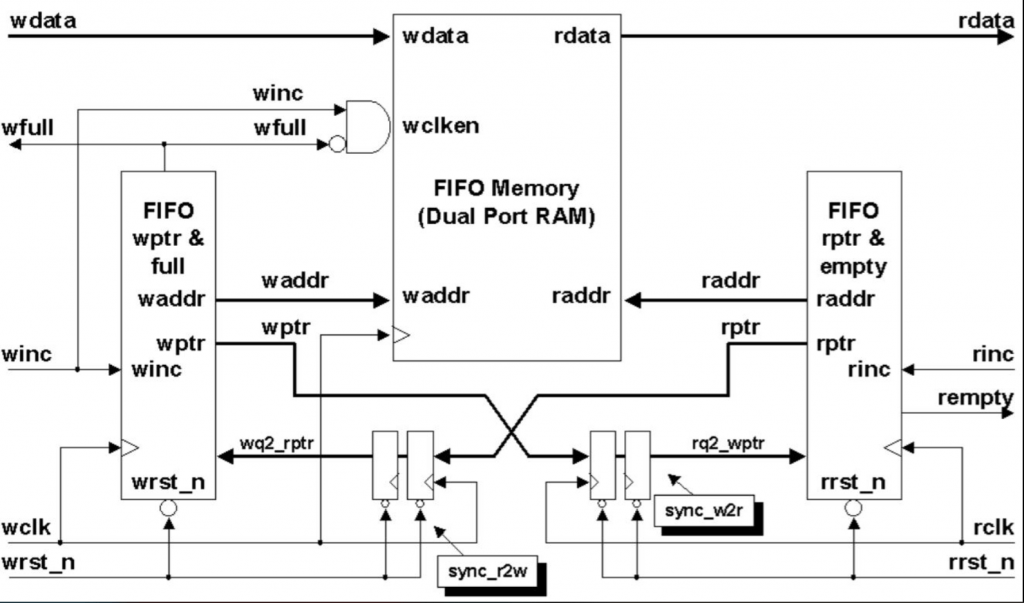

如上圖

interface 可切分為左半邊 write 端

- wdata : write data,寫入資料的bus

- wfull : write full, FIFO已經滿的訊號

- winc : write data valid,寫入資料的有效訊號

- wclk : write clk,寫入端的 clk domain

- wrst_n : write rst_n,寫入端clk的rst_n

右半邊的 read 端

- rdata : read data,讀取資料的bus

- rempty : read empty, FIFO已經空的訊號

- rinc : read data enable,讀取一筆資料的有效訊號

- rclk : read clk,讀取端的 clk domain

- rrst_n : read rst_n,讀取端clk的rst_n

最主要儲存資料的 FIFO memory 可以使用 register 或是 dual port(two clk) sram

wptr 和 rptr 分別是 write pointer 和 read pointer

為了避免 crossing clock domain 造成同時超過一筆訊號 metastable 的情況

wptr 和 rptr 必須要以 gray code 來做轉變

而 wptr 需要經過兩級 read clk domain 的 DFF 傳遞到 read 端

rptr 需要經過兩級 write clk domain 的 DFF 傳遞到 write端

再透過 rq2_wptr 和 rptr 的比較來做出 read empty 訊號

同時也透過 wq2_eptr 和 wptr 的比較來做出 write full 訊號

這樣外部就可以根據這兩個訊號來判斷是否可讀和可寫

在寫入端可以使用一個 and gate 將 winc 和 ~wfull and 起來

以避免外部 overwrite 的狀況

發表留言